IEEE Standard 754 Floating Point Numbers Multiplier

IEEE 754 Floating Point Multiplier是一個基於Verilog的設計,使用有限狀態機結構實現。其主要功能是接收兩個浮點數,將它們相乘,然後輸出IEEE 754格式的乘積浮點表示。這個專案使用了8個不同的狀態,每個狀態負責不同的運算和數據處理任務。

Project Details

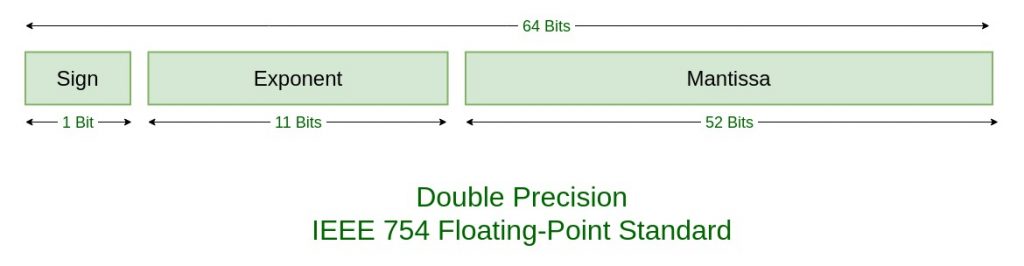

IEEE 754 Floating Point Multiplier專案的目標是用Verilog實現一個能夠有效處理浮點數相乘並且可以合成的電路。IEEE 754是一種標準的浮點數表示方式,它包含了三個部分:符號位(sign bit)、指數部分(exponent)、和小數部分(fraction)。我們的設計需要處理這三個部分,並實現浮點乘法的運算。

Specification

- It is active-high synchronous reset architecture

- The rounding mode is round to nearst

- You should try to maximize the operation frequency of this pipeline floating multiplier

- The output latency after data input should be smaller than 60 clock cycles

I/O Defination

| Signal Name | Direction | Bit Width | Description |

|---|---|---|---|

| CLK | Input | 1 | Clock signal |

| RESET | Input | 1 | Synchronous reset signal (active high) |

| ENABLE | Input | 1 | Asserted when input data is vaild |

| DATA_IN | Input | 8 | The data will input when ENABLE is high |

| DATA_OUT | Output | 8 | Output data |

| READY | Output | 1 | Asserted when DATA_OUT is vaild |

Design

這個專案的核心結構是有限狀態機(finite state machine),它共包含8個不同的狀態,每個狀態都負責不同的任務。以下是每個狀態的主要功能:

- Idle:在閒置狀態下,所有的值都被歸零,準備接收新的輸入。這包括清除暫存器、重置接線、和輸出控制訊號

- DataIn:這個狀態用於將輸入的浮點數資料分別存儲至 A 和 B,準備進行後續的運算

- Unpack:根據IEEE 754格式,將輸入的浮點數資料拆解為符號位(sign)、指數(exponent)和小數部分(fraction)

- Mul0:使用Chip Wise乘法器對A和B的小數部分(fraction)進行乘法運算

- Mul1:處理符號位(sign bit)以及對指數(exponent)進行加法運算

- Norm:這個狀態負責處理溢位,確保結果在浮點數表示的有效範圍內,同時進行四捨五入運算

- Pack:將計算結果分成8組,準備進行後續的輸出

- Output在最終的狀態下,將計算結果以IEEE 754浮點表示輸出

Achievements Display

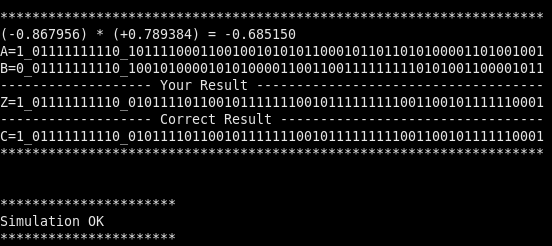

RTL Simulation.

RTL Simulation.

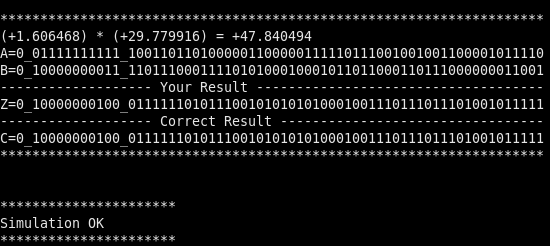

Netlist Simulation.

Netlist Simulation.

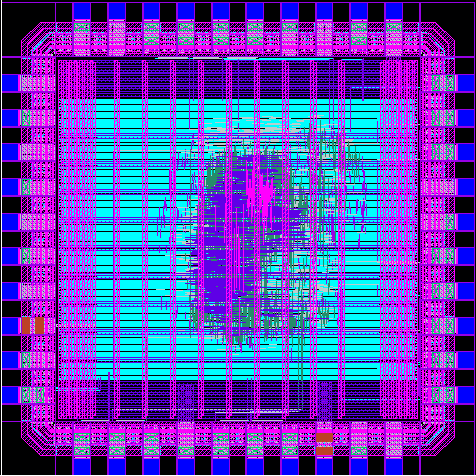

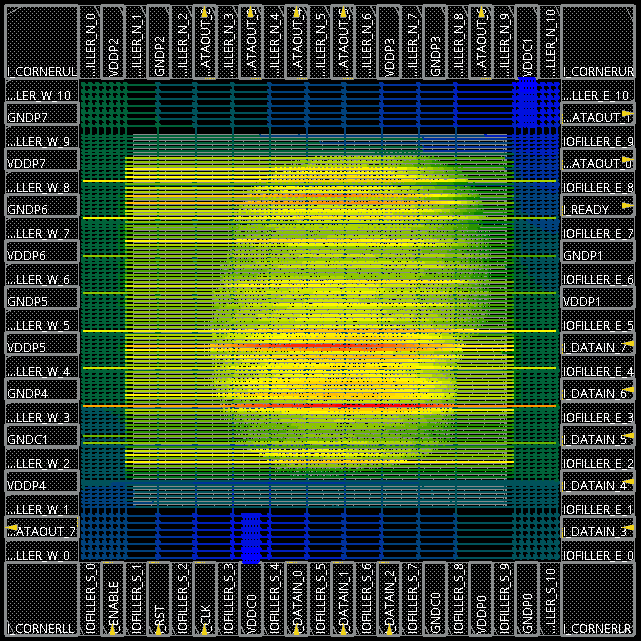

CHIP Layout.

CHIP Layout.

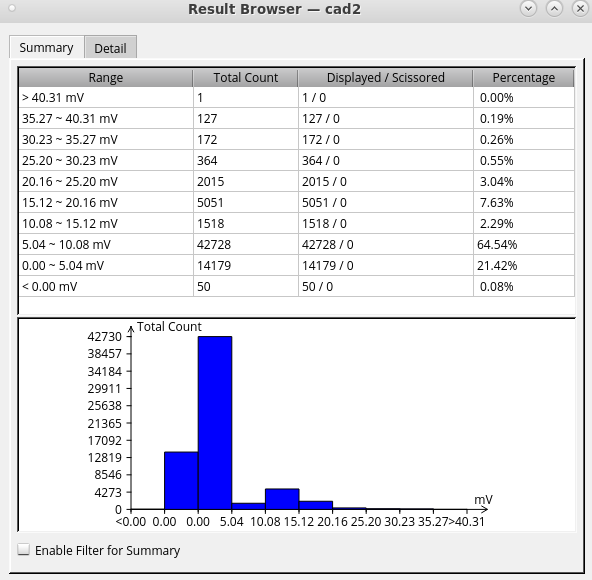

Power Rail Analysis.

Power Rail Analysis.

Power Rail Analysis.

Power Rail Analysis.

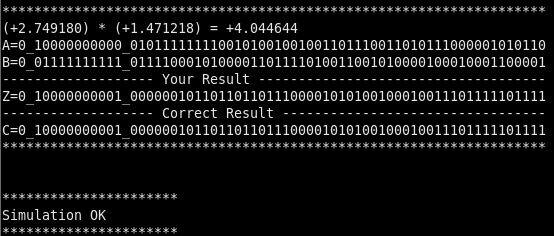

Post Layout Simulation.

Post Layout Simulation.